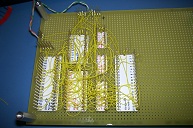

Version 1

Version 1 is a minimal hardware configuration that will run Altair BASIC. It consists of an 8085 CPU, a RAM chip, a 6850 UART, a latch and some glue logic and a PIC microcontroller. On power up the PIC loads the Altair bootloader into RAM, then resets the 8085 and starts it running. BASIC can then be loaded through the 6850 serial port.

Theory of Operation

The core system consists of the CPU, Memory, and UART. The PIC microcontroller is used the pre-load the RAM while holding the 8085 using the HOLD line. When the 8085 RESET line is released, it starts running at location 0.Schematic

Note the schematic does not show all the power supply and ground connections to the chips or the bypass capacitors.CPU

The 8085 was chosen because it is software compatible to the 8080A but is easier to use because of the following improvements:- The 8085 requires a single +5V power supply. The 8080A requires three supplies: +5V, +12V and -5V.

- The 8085 has a built in clock generator, requiring only an external crystal. The 8080A required two non-overlapping +12V clock signals.

- The 8085 multiplexes the address and data bus which requires a simple latch to demultiplex. The 8080A multiplexes the status signals onto the data bus.

- The 8085 uses TTL compatible logic levels. The 8080A logic levels are not standard TTL.

The 8085 runs at 3 MHz clock frequency with a 6 MHz crystal. The HOLD line is used by the PIC to share the memory and UART with the 8085. When the HOLD line is asserted, the 8085 address, RD, WR, and IO/M lines are tri-stated.

Address Latch

The lower 8 bits of the address is latched off of the data bus with a 74LS373. The latch is clocked by LE. LE is pulsed either by the PIC MCUALE line or at the beginning of each machine cycle by the 8085 ALE line.Memory

32K bytes of static RAM is provided by a CY62256. The memory can be accessed by either the 8085 or the PIC. The RD and WR lines are connected to both the 8085 and the PIC tri-state outputs in a wired-or fashion. The RAM is enabled by RAMCE when the address is in the lower 32KB of the address space and the current CPU cycle is a memory access (not an IO cycle).UART

The 6850 UART can be accessed by either the 8085 or the PIC. UCLK is the baud rate clock which is generated by the PIC. The 6850 bus interface is clocked by the E line which is driven by UE. UE is asserted whenever RD or WR go low. The 8085 status signal S1 provides an early R/W signal that is stable when E is pulsed. S1 is multiplexed with MCUS1 from the PIC depending on the state of the HOLD line. The resulting US1 drives the UART R/W input. The UART is intended to be mapped to IO addresses 020 and 021 (octal). Actually only address bits A0, A4 and A7 are decoded, so the UART will respond to any addresses 0XX1XXX0 and 0XX1XXX1. RxData and TxData are 5V RS232 lines and must be converted by a level shifter like a MAX232 to connect to a true RS232 terminal or a PC serial COM port.PIC

The PIC18F320 microcontroller performs several functions. It runs off it's internal oscillator at 8 MHz (2 MIPs).- It uses a PWM peripheral to generate the baud rate clock for the UART, output UCLK. This clock is 16 times the baud rate. For 9600 baud, it is 153.6 kHz.

- It is connected to the address bus and data bus and can control the UART and RAM. At power up it loads the RAM with the Altair bootloader and outputs a message with the UART.

- It controls the 8085 READY line which idles the 8085 and forces it to float the address, RD, WR and M/IO lines

- It controls the 8085 RESET line. When RESET is released, the 8085 starts running at address 0.

- It mimics the Altair sense switches. This PIC has a PSP (Parallel Slave Port) peripheral which is an 8 bit parallel port with asynchronous RD and WR and CS inputs. The MCUCS line is decoded when address bit 7 and an IO operation is taking place. If the 8085 reads IO address 377 octal (the location of the sense switches), it will read the PSP. The PIC pre-loads the PSP with the sense switches setting. This function is necessary because Altair BASIC reads the sense switches to determine which UART driver code to use. Since only address bit A7 is decoded, any access to IO addresses 1XXXXXXX will access the sense switches register.