Version 4

Version 4

Version 4 side view

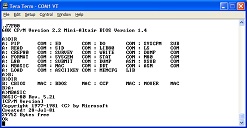

Screen Shot of Booting CP/M

Version 4 expands the RAM from 32K to 64K. This allows

versions of

CP/M that are configured for more than 32K of RAM to run.

Theory of Operation

RAM chips

To avoid adding another socket and more wiring, the second 32K RAM chip

is just stacked on top of the first chip. All the pins are

soldered in parallel, except the chip select pins. The

address decoding logic for the RAM was modified to provide separate

chip select signals for each chip depending on the state of A15.

Note

the schematic does not show all the power supply and

ground connections to the chips or all the bypass

capacitors.

The

CP/M from the

Altair32 software package was used. Trying to

boot using the CP/M disk images in the package results in the system

hanging after outputting the welcome message. Examining the

CBIOS source code file provided in the package shows that the problem

is caused by the BIOS resetting the console port after it outputs the

welcome message. Sending the reset byte to the UART resets

the baud rate clock divider and the number of stop bits and should be

followed by sending another byte that initializes these to the correct

values. But only the reset byte is sent, so the UART doesn't

function after this point. The solution is to NOP out the

reset instruction bytes. This requires modifying the disk

image. The reset bytes are NOP'ed out and the welcome message

is changed. The ROM disk bootloader checks a checksum byte

for each sector it reads, so these bytes must also be changed for the

modified image to boot.